VHDL & Verilog Programming. Complete circuit of full-adder and half-adder with truth table and detailed discussion of verilog code.

Full adders are a basic building block for new digital designers. Lots of introductory courses in digital design present full adders to beginners. Once you understand how a full adder works, you can see how more complicated circuits can be built using only simple gates. I just want to make it clear to someone new that in reality, FPGA designers are not coding full adders by hand. The tools are advanced enough to know how to add two numbers together. It's still a good exercise, which is why it is presented here.

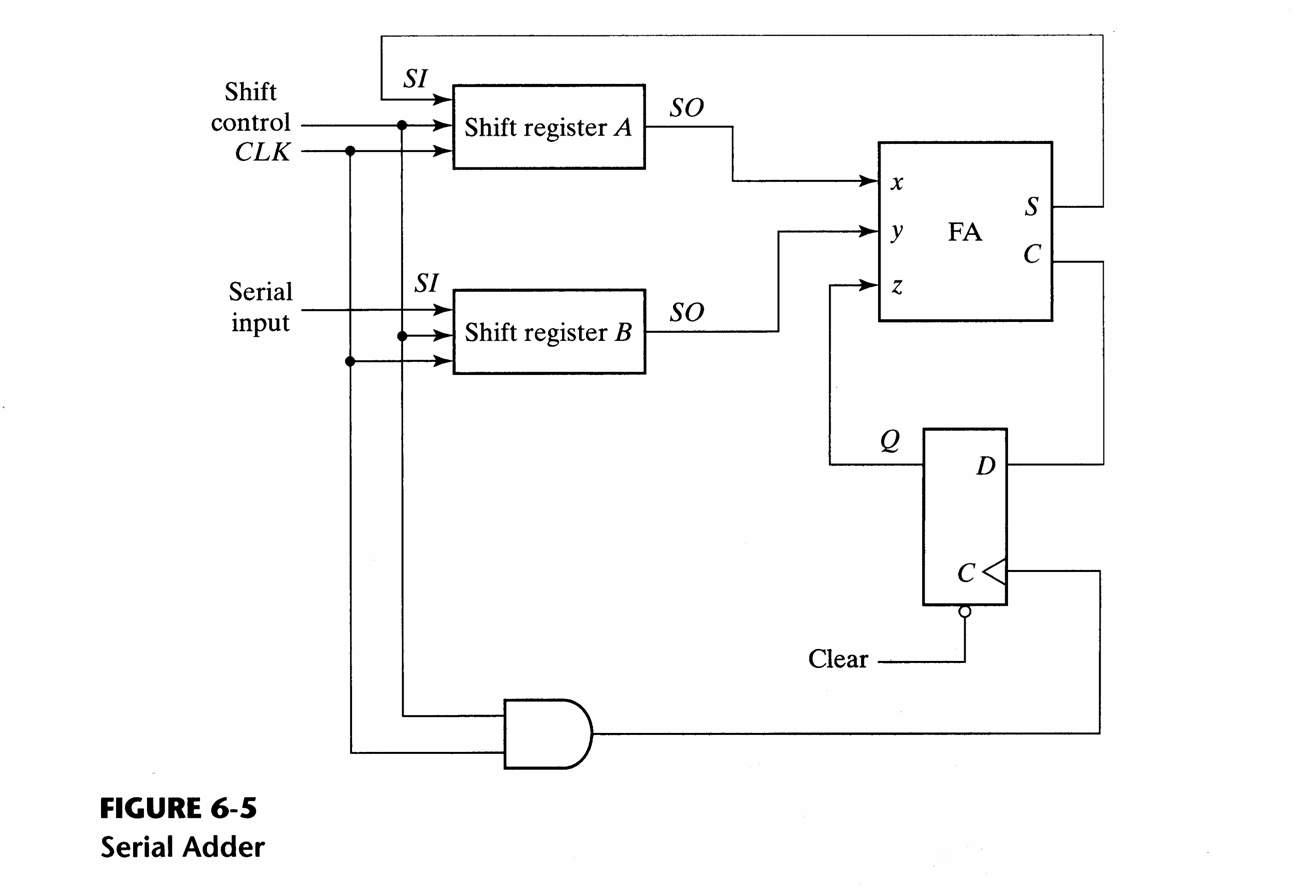

A single full-adder has two one-bit inputs, a carry-in input, a sum output, and a carry-out output. Many of them can be used together to create a ripple carry adder which can be used to add large numbers together. Feg pa 63 serial number lookup. A single full-adder is shown in the picture below.

The next picture shows the entire schematic of the full adder and its corresponding truth table. The red text ties into the code below. w_WIRE_1, w_WIRE_2, w_WIRE_3 are the intermediate signals shown in the red text on the schematic.

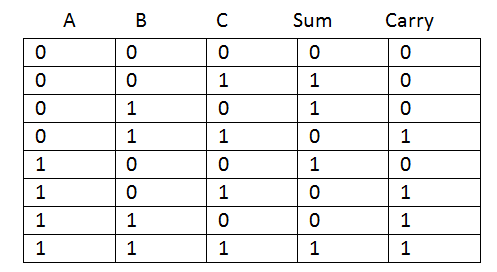

| Full Adder Truth Table | ||||

|---|---|---|---|---|

| A | B | Cin | Cout | Sum |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

VHDL Implementation:

full_adder.vhd:

Verilog Implementation:

full_adder.v:

Help Me Make Great Content! Support me on Patreon! Buy a Go Board!

//Verilog code for 8:1 Multiplexer using 4:1 Multiplexer and 2:1 Multiplexer

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: RED-BLUE

// Engineer:

// Create Date: 16:14:30 11/09/2016

// Designer Name: Madhu Krishna

// Module Name: mux81_u_mux41

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module mux81_u_mux41(input_d0,

input_d1,

input_d2,

input_d3,

input_d4,

input_d5,

input_d6,

input_d7,

sel_0,

sel_1,

sel_2,

output_y);

// INPUTS

input input_d0;

input input_d1;

input input_d2;

input input_d3;

input input_d4;

input input_d5;

input input_d6;

input input_d7;

input sel_0;

input sel_1;

input sel_2;

// OUTPUT

output output_y;

wire [1:0] mux_com_out;

// Declaration of 8:1 mux using 4:1 mux and 2:1 mux

// MUX 4:1 Instantiation Template

mux4_1_code U_MUX4_1_1 (

.input_d0(input_d0),

.input_d1(input_d1),

.input_d2(input_d2),

.input_d3(input_d3),

.sel_0(sel_0),

.sel_1(sel_1),

.output_y(mux_com_out[0])

);

mux4_1_code MUX4_1_2 (

.input_d0(input_d4),

.input_d1(input_d5),

.input_d2(input_d6),

.input_d3(input_d7),

.sel_0 (sel_0),

.sel_1 (sel_1),

.output_y(mux_com_out[1])

);

// MUX 2:1 Instantiation Template

mux2_1_code U_MUX2_1_1 (

.input_a(mux_com_out[0]),

.input_b(mux_com_out[1]),

.sel_0 (sel_2),

.output_y(output_y)

);

System Verilog Adder

// Create Date: 16:14:30 11/09/2016

// Designer Name: Madhu Krishna

// Module Name: mux81_u_mux41

// Project Name:

// Target Devices:

// Tool versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module mux81_u_mux41(input_d0,

input_d1,

input_d2,

input_d3,

input_d4,

input_d5,

input_d6,

input_d7,

sel_0,

sel_1,

sel_2,

output_y);

// INPUTS

input input_d0;

input input_d1;

input input_d2;

input input_d3;

input input_d4;

input input_d5;

input input_d6;

input input_d7;

input sel_0;

input sel_1;

input sel_2;

// OUTPUT

output output_y;

wire [1:0] mux_com_out;

// Declaration of 8:1 mux using 4:1 mux and 2:1 mux

// MUX 4:1 Instantiation Template

mux4_1_code U_MUX4_1_1 (

.input_d0(input_d0),

.input_d1(input_d1),

.input_d2(input_d2),

.input_d3(input_d3),

.sel_0(sel_0),

.sel_1(sel_1),

.output_y(mux_com_out[0])

);

mux4_1_code MUX4_1_2 (

.input_d0(input_d4),

.input_d1(input_d5),

.input_d2(input_d6),

.input_d3(input_d7),

.sel_0 (sel_0),

.sel_1 (sel_1),

.output_y(mux_com_out[1])

);

// MUX 2:1 Instantiation Template

mux2_1_code U_MUX2_1_1 (

.input_a(mux_com_out[0]),

.input_b(mux_com_out[1]),

.sel_0 (sel_2),

.output_y(output_y)

);

System Verilog Adder

endmodule